# Supplementary Materials for

#### Complete active-passive photonic integration based on GaN-on-silicon platform

Jiabin Yan\*a, Li Fanga, Zhihang Suna, Hao Zhanga, Jialei Yuana, Yan Jianga, and Yongjin Wang\*a

- <sup>a</sup> Peter Grünberg Research Center, Nanjing University of Posts and Telecommunications, Nanjing 210003, China

- \* Correspondence to: jbyan@njupt.edu.cn, wangyj@njupt.edu.cn

#### S1. Fabrication processes of the photonic integrated chip.

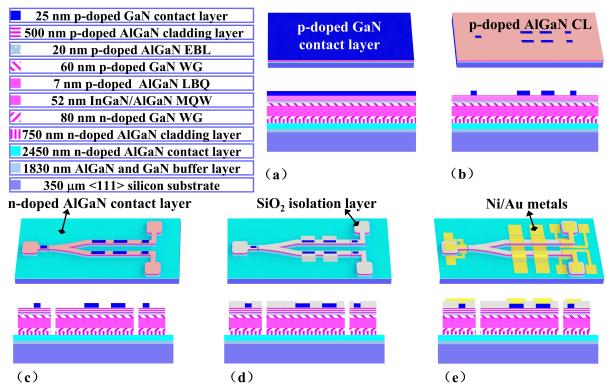

**Figure S1. Fabrication flow of the photonic integrated chip.** Inset in top left corner shows the epilayer structure of the wafer. (a) Wafer preparation. (b) ICP etching with the p-doped AlGaN cladding layer exposed. (c) Deep ICP etching with the n-doped AlGaN contact layer exposed. (d) SiO<sub>2</sub> grown by the plasma enhanced chemical vapor deposition and patterning by the buffered oxide etch solution. (e) Electrodes deposition by the electron beam evaporation and patterning by the lift-off process.

Step one is wafer preparation, as shown in Figure S1(a). The III-nitride epilayers with a total thickness of 5.77 µm are deposited by MOCVD in the c-axis direction. The silicon substrate is

thinned and polished to a thickness of 200 µm. Then the 2-inch wafer is diced to 4 small chips with size of 2 cm × 2 cm. The small chip is prepared for the following fabrication processes. Step two is inductively coupled plasma (ICP) etching to pattern the p-contact region of the MQW diodes, as shown in Figure S1(b). The coated AZ5214 photoresist with a thickness of 1.6 µm is used as the masking material. 100 W RF power and 300 W DC power are adopted for the etching. The plasma chemistry for the process is set at 10 sccm Cl<sub>2</sub>/25 sccm BCl<sub>3</sub>, while the temperature and pressure are maintained at 20 °C and 5 mTorr, respectively. The etching depth is 160 nm and the p-doped AlGaN cladding layer is exposed for the region without the protection of photoresist. Step three is ICP etching to form the MQW diode and waveguide devices, as shown in Figure S1(c). The coated AZ4620 photoresist with a thickness of 6.5 μm is used as the masking material. 100 W RF power and 300 W DC power are adopted for the etching. The plasma chemistry for the process is set at 10 sccm Cl<sub>2</sub>/ 25 sccm BCl<sub>3</sub>, while the temperature and pressure are maintained at 20 °C and 5 mTorr, respectively. The etching depth is 1.6 µm and the silicon substrate is exposed for the region without the protection of photoresist. Step four is deposition of SiO<sub>2</sub> layer with a thickness of 100 nm by PECVD, as shown in Figure S1(d). The SiO<sub>2</sub> layer is pattered by the tetramethylammonium hydroxide (TMAH) solution treatment and used as the insulation layer. Step five is deposition of Ni/Au layers with thickness of 20/200 nm, as shown in Figure S1(e). The metal electrode is patterned by the lift-off technology and subsequently treated by the rapid thermal annealing (RTA) at 550 °C for 60 s in N2 ambient to improve the ohmic contact performance. Finally, separate PIC chip is obtained by dicing the wafer using a dicing saw (DISCO DAD3350).

### S2. Supplementary results.

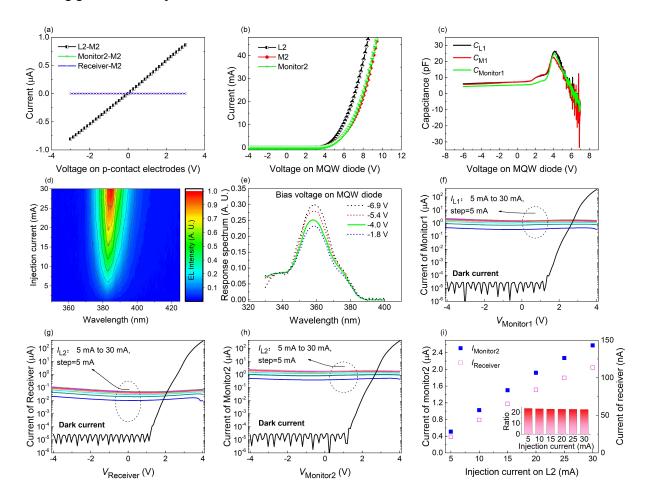

Figure S2. (a) Leakage currents between the p-contact electrodes. (b) IV characteristics of L2, M2, and Monitor2. (c) CV characteristics of L1, M1, and Monitor1. (d) EL intensities under different injection currents. (e) RS under different applied bias voltages. (f) Detected photocurrent of monitor1 under different injection currents on L1. (g) Detected photocurrent of the receiver under different injection currents on L2. (h) Detected photocurrent of monitor2 under different injection currents on L2. (i) Detected photocurrent of the receiver and monitor2 versus the injection currents on L2.

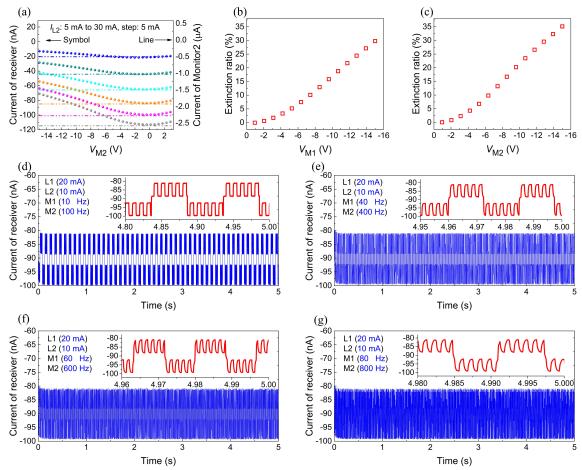

**Figure S3.** (a) Detected photocurrents versus the bias voltages on M2. (b) Extinction ratio of the up branch versus the applied voltage on M1. (c) Extinction ratio of the low branch versus the applied voltage on M2. (d) Received waveform of the receiver when two modulation signals with different frequencies (10 and 100 Hz) are simultaneously applied on the modulators. (e) Received waveform of the receiver when two modulation signals with different frequencies (40 and 400 Hz) are simultaneously applied on the modulators. (f) Received waveform of the receiver when two modulation signals with different frequencies (60 and 600 Hz) are simultaneously applied on the modulators. (g) Received waveform of the receiver when two modulation signals with different frequencies (80 and 800 Hz) are simultaneously applied on the modulators.

## S3. EL and responsivity spectra characterization.

The PIC chip was bonding to a customized PCB. The responsivity spectra were measured using the Oriel IQE-200B (Newport Corp), in which a Xenon lamp is used as the light source,

and a calibrated reference detector provides reliable and repeatable calibration. For the EL measurement, the emitted light was coupled into a 200-µm-in-diameter multimode fiber by a lens system and fed to an Ocean Optics HR4000 spectrometer for characterization.

#### S4. Electrical testing method.

The Agilent Technologies B1500A semiconductor device analyzer was used to provide the bias voltage and measure the photocurrent and capacitance. The incident square wave and PRBS data were generated by the Keysight 33600A series waveform generator. The Keysight DSOS604A digital storage oscilloscope was used to collect and display the eye diagram. The Keithley 2636B system source meter was used to provide the injection current for the light sources (L1 and L2).